Verilog-Aはモデリング言語ですが、シミュレーションの時のちょっとした信号変換モジュールを作成するのにも活用できます。この記事では、ミニツールの作成として、Verilog-Aを用いた回路設計に便利な「単相差動変換ブロック」を紹介します。

QucsStudioを用いたVerilog-Aモデルの利用方法については、次の記事を参考にして下さい。

[pagelink id=1366]

概要

電子回路を組んでいると、単相信号を差動信号に変換したい要求が出てくることがあります。そういったことを回路で実装する場合、バランを用いたり、アンプを用いる訳ですが、こういった素子を利用する場合、理想的な挙動は得られず、変換回路が悪いのか、実装が悪いのか、分からなくなってしまいます。

こういった差動単相変換回路が理想素子であると、回路設計の際に便利です。そこでVerilog-Aでそういった変換回路を組んでみることにします。

仕様

単相差動回路は、入力信号のコモン電圧と出力信号のコモン電圧が分かれば簡単に構築できます。

入力信号をVin、出力信号をVoutp、Voutnとすると、以下の式が成立します。ただし、Vin_thは入力信号のコモン電圧、Vout_cmは出力信号のコモン電圧とします。

- 変換条件:(Voutp-Vout_cm)-(Voutn-Vout_cm) = Vin - Vin_th

- 差動条件:Voutp = -Voutn

上記を解けば、以下の式が出てきます。

- Voutp = -Voutn = (Vin - Vin_th) / 2

あとはこれを記述すれば良いことになります。

パラメータとして、入力信号のコモン電圧vthと出力信号のコモン電圧voutcmを取ることにします。

実装

上記をVerilog-Aで記述すると、以下の様になります。

`include "disciplines.vams"

`include "constants.vams"

// Module name becomes name of the model file names.

module s2d (in, outp, outn);

inout in, outp, outn;

electrical in, outp, outn;

`define attr(txt) (*txt*)

parameter real vth=0 from [-inf:inf] `attr(info="input threshold voltage" unit="V");

parameter real voutcm=0 from [-inf:inf] `attr(info="output common voltage" unit="V");

real vin, voutp, voutn;

analog begin

vin = V(in) - vth;

V(outp) <+ vin/2 + voutcm;

V(outn) <+ -vin/2 + voutcm;

end

endmodule

評価結果

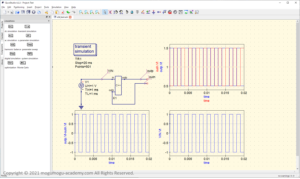

上記モジュールを評価するのは時間軸評価で十分でしょう。Qucsで実装して、実行結果を確認することにします。

ベンチと実行結果を以下に示します。入力信号のスレッショルドは0V、出力信号のコモン電圧は1Vと設定しています。入力は-1~+1Vの矩形波としています。

上記に示すように、単相信号を差動信号に変換することが出来ました。正ノードであるoutpと負ノードであるoutnの電圧ノートの振幅自体はinの振幅の半分である0.5~1.5Vであることが確認できます。outpとoutnの差をグラフ化すると、入力と波形が一致しています。

終わりに

今回はVerilog-Aを利用した単純なツールの作成を実例として紹介しました。

単相差動変換は活用する機会が多い信号変換ですが、Spiceの標準機能だけで理想素子の実現をするのは少し面倒です。今回はVerilog-Aを用いることで、短いソースコードで簡潔に、単相差動変換を表現することが出来ました。

こういった工夫で回路設計は効率的になりますから、是非、自前のIP構築の参考にして下さい。