始めに

現代の製品開発において、高位モデルは非常に重要です。高位モデルを活用することで、実装作業なしに必要なスペックを決定することが出来たり、最終的な性能への影響を評価することが出来るからです。

回路シミュレータであるSpiceなどにおいて、高位モデルを作成するためには、電圧制御電圧源や電圧制御電流源を活用して構築する方法がありました。しかし、これでは効率が悪いだけでなく、記述できない内容も多数ありました。そこで、高位モデルを記述する方法が求められていました。

電子工学の世界では、Verilogが事実上の業界標準となっている様相を呈していることから、アナログモデリングに向けて拡張したVerilog-A、そしてそれを進展させたVerilog-AMS、といった規格が普及しています。Verilog-AMSはVerilog-Aの拡張ではありますが、組み込み関数の記述法が異なったり、完全な互換性は無い様です。Verilog-AにせよAMSにせよ、規格化はされていますが、IEEEの様な標準団体によって標準化された物ではない、という所に注意が必要です。

なお、自動車工学の世界では、国際標準団体によって標準化された物が重要であるからか、VHDL-AMSが広く使われている様です。VHDLは仕様書策定言語から始まった言語で、厳格な記述が特徴でした。一方で、仕様上、Verilogに比べ、シミュレーションの実行速度が遅くなりがち、という欠点がありました。

Verilog-A(MS)にせよ、VHDL-AMSにせよ、現在、完全にフリーで活用出来る環境というのは中々ありません。業務でやっている場合は商用ツールがあるので良いのですが、勉強で少し使ってみたいだけの場合、ハードルが高い状況でした。

今回、Verilog-Aが利用できるフリー(無料)の環境を見つけることが出来たので、共有したいと思います。Verilog系統であるVerilog-Aは、現状の電子回路シミュレータと相性が良く、電子回路エンジニアが学ぶのに非常に適しています。

ただ、最初に伝えておく必要がありますが、残念ながらQucsStudioで利用できるVerilog-Aには非常に制限が大きいという現状があります。正直、とてもではありませんが、実用で使えるレベルのVerilog-A記述が出来るとは思えません。しかし、デバイスモデルを開発しているのであれば、話は別です。Verilog-Aで「デバイスモデルを開発する」というのであれば、QucsStudioは選択肢の一つとして挙げられます。

そういったことを念頭に置いて、Verilog-Aによるモデリングの世界を体験してみてください。

QucsとQucsStudioの比較

QucsStudioはQucsのほぼ上位互換

QucsStudioはQucsを基に作られた派生版のシミュレータです。基本的に、Qucsのソースコードをベースにして、機能追加を施してあります。

ですから、QucsStudioはQucsのほぼ完全上位互換であると言えます。加えて、Qucsでオプション扱いだったものもQucsStudioではデフォルトでインストールされていたり、と利便性の向上も図られています。

正直な所、QucsStudioの機能をQucsが取り込んでいないのが理解できないほど、QucsStudioは便利になっていると思います。加えて、LineCalcなどの伝送線路計算アプリもついている様なので、高周波設計ではQucsStudioの方が絶対便利でしょう。

なお、QucsとQucsStudioのシミュレーションエンジンは全くの別物ということなので、あくまでも「使い勝手面」について、上位互換、と考えるべきでしょう。

Verilog-A事情

QucsもVerilog-Aモデルに対応していないわけではありません。QucsもVerilog-Aで記述されたモデルを取り込むことが出来ます。しかし、動的に取り込めず、再コンパイルが必要、というのが最大の弱点です。流石に、毎回Qucs全体を再ビルドする、というのは、開発負荷が大きく、試しで使うのもはばかられます。もちろん、Qucsもそういった事情は理解しており、「Verilog-A dynamic loader」の開発には取り組んでいる様です。しかし、Qucsではまだ実現できていない様です(少なくても)。

QucsStudioはQucsをベースとして開発しながら、Verilog-Aの動的ロードに対応しています。これはVerilog-Aコードを取り込む際にシミュレータ全体の再コンパイルが不要となることを示しています。これはVerilog-Aを活用する上で、非常に便利です。

こういった背景から、Verilog-Aを試すのであれば、QucsStudioを活用すべきであると言えます。

Verilog-Aの実現方法

QucsでもQucsStudioでも、Verilog-Aを実現するにあたり、外部のツールの力を活用しています。ツールチェインとしては、Verilog-A言語のサブセットからC言語ソースコードを生成する「ADMS」を実行し、それをCコンパイラでコンパイルする形式をとっています。

Qucsではツール自体に組み込むために「生成されたソースコードをツールのソースに組み込んだ後、コンパイル」していましたが、QucsStudioは「生成されたソースコードをコンパイルして共有ライブラリを生成」しています。これにより、動的ロードを実現しています。

QucsStudioのインストール方法

これまで説明したように、基本的にQucsStudioはQucsの上位互換となっています。そして、インストール方法などもQucsと変わりません。ただし、QucsStudioはWindows限定のツールという違いがあります。

QucsStudioのページは以下の二つがあります。

ダウンロードはどちらからでも大丈夫ですが、たまにリンクが切れていたりするので、ダウンロードできる方を使えば良いでしょう。2021年9月現在、前者のリンクが切れている様でしたが、後者からは問題なくダウンロードできました。

なお、インストール方法や簡単な使い方は、以下を参考にして下さい。

-

Qucsのインストールとネットリスト互換性

続きを見る

[ignore]721へリンクを張る[/ignore]

Verilog-Aモデルの使い方

[ignore]画面をキャプチャしながら、使い方を説明する[/ignore]

それでは、QucsStudioにおいて、Verilog-Aモデルを使う方法について、説明します。Verilog-Aモデルを使用するためには、「Verilog-Aコードの記述」と「回路図へのモジュールの配置」が必要となります。Verilog-Aコードについては自分で記述する必要がありますが、回路図に配置するシンボル自体はVerilog-Aコードより自動で作成されます。

1. Verilog-Aコードの追加と記述

Verilog-AコードとしてQucsStudioに認識してもらうためには、ファイル名の拡張子がvaでなければいけません。逆に、.vaファイルを追加すれば、自動的にVerilog-Aモデルとして認識される、ということでもあります。

なので、最も簡単な方法は、「File→New→New Text」で追加のテキストファイルを表示し、そのファイルを保存する時に拡張子を.vaとして保存することです。これで簡単にVerilog-Aファイルを追加することが出来ます。

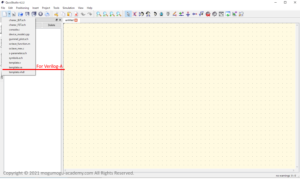

もう一つの方法は、テンプレートを適用したファイルを新規作成する方法です。これは、メニューバーからの操作は出来ない様ですが、操作用のボタンで実施出来ます。テンプレートを用いることで、比較的簡単にVerilog-Aのコードを追加することが出来ます。

このテンプレートはデフォルトでは、バイポーラトランジスタの簡便なモデルが設定されています。また、コメントも適切に書いてあるので、初学者でも使いやすい形になっています。

2.回路図へのモジュールの配置

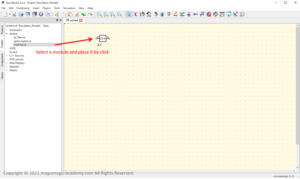

「Content」から「Verilog」のツリーを開き、その中で配置したいモジュールを選択します。そのあと、スケマティック部で再度クリックすれば、選択されたモジュールが配置されます。

シンボルが自動生成されるため、ポート位置を調整することは出来ない様です。ただ、サブサーキットを用いて、くるんでやれば、簡単に自分の欲しいシンボルを利用することが出来ます。ですから、そこまで困らず使えるでしょう。

シンボルが自動生成されるため、ポート位置を調整することは出来ない様です。ただ、サブサーキットを用いて、くるんでやれば、簡単に自分の欲しいシンボルを利用することが出来ます。ですから、そこまで困らず使えるでしょう。

QucsStudioにおけるVerilog-Aの制限

変数の型の制限

変数の型に色々と制限があります。自分が確認した段階では以下が制限されている様です。

- inoutのみ使用可能:input, outputは使用不可

- electricalのみ使用可能:current, voltageは使用不可

これらについては、上位互換である指定子が使用可能なので、そこまで困らないでしょう。

条件分岐使用不可

条件分岐に非対応です。そのため、if文やcase文を用いたモデルは構築することが出来ません。境界領域の挙動をif文で記述しようとしている場合、滑らかな関数でフィッティングするなど、小細工が必要となります。

通常のアナログモデルは、伝達関数や微分方程式の形式でモデルが記述されるため、この制限も用途によっては困らないでしょう。

アナログイベントの制限

アナログイベントとは、初期化や信号のクロスの検出などを挿します。アナログイベントに応じて、モデリングされたモジュールは動作を変えることが出来ます。

アナログイベントとして、良く使用される例としては、クロック検出です。閾値を基準として、立ち上がり・立ち下がりを検出し、それにより動作を変えることが出来ます。サンプル・アンド・ホールド回路でよく使われそうな機能です。

微分方程式記述の制限

微分方程式の記述についても制限があります。これはツールチェインとして組み込まれているADMSの制限のため、QucsStudioの開発としては手が付けづらい状況です。ADMSは長期間大規模修繕がされていない様なので、修正は難しいかもしれません。

以下に制限を紹介します。なお、原文は以下の参照リンクからPDFを見て下さい(英語)。

Qucs A Description Verilog-AMS interface, Qucs SourceForge

代入時の電流と電荷の式の混在禁止

「代入文において、電流と電荷の式を混ぜること」は禁止されています。この挙動は明らかにバグ的な動作であり、Verilog-Aモデルの使用を困難にしています。このバグの最大の問題は、コンパイル時に検出が出来ない、ということです。本来、微分要素と定数要素を分離して、シミュレータのソルバー(数値演算器)に渡さないといけない様ですが、それが出来ていない、というのが問題です。

以下にQucsで掲載されているコードの例を載せます。微分部分と定数部分を分離して、記述してやれば、正常に動作する、ということです。

// NG I(a,c) <+ Id + ddt(Cap*V(a,c)); // OK I(a,c) <+ Id; I(a,c) <+ ddt(Cap*V(a,c));

右辺での即値電位の禁止

右辺に即値電位を使用する場合、正常にコンパイルが出来ません。条件によっては出来るのですが、出来ないこともあるので、使用しない方が賢明です。また、これもコンパイルエラーが出ない系バグです。

即値電位とは電圧表現のことで、平たく言うと「V()オペレータ」といってよいでしょう。微分方程式を表現する<+オペレータ文中の右辺でV()は使用してはいけない、という制限と言えます。

以下にNGの例とOKの例を示します。

Is=1e-15; // NG I(a,c) <+ Is + (exp(V(a,c)/26e-3)-1); // OK Id = Is * (exp(V(a,c) / 26e-3)-1); I(a,c) <+ Id;

[Qucsのみ]左辺での電圧参照禁止

QucsStudioではバグ修正されている様ですが、Qucsでは左辺で電圧参照するのが禁止されていました。以下に例を示します。

// NG V(a,c) <+ I(a,c) * 100; // OK I(a,c) <+ V(a,c) / 100;

利用可能関数は限定的

QucsStudioで利用可能な関数は限定的です。システムに関連する関数はサポートされていませんし、その他の関数でもサポートされていない可能性があります。

この点は調べ切れていないので、関数を使用する場合には注意をして下さい。関数がサポートされていない場合、Cコードをコンパイルする段階でエラーが出てくるはずなので、その点は安心できます。

QucsStudio対応のコーディングルール

以上を参考に、QucsStudio対応のコーディングルールをまとめます。

- 入力ポートの宣言はinout, electricalで定義する

- 条件分岐は使用しない

- アナログイベントはinitialのみ使用可能

- ノード電位はreal変数を経由して参照する

- [Qucs]左辺にV()を使わない

基本的にアナログ文ではVを使わず、ノード電位を参照する際には必ずreal変数を経由する、というのが重要です。これについては、コンパイルエラーで検出できないため、意識しておく必要があります。

QucsStudioでのVerilog-A活用法

これまで見てきたように、Verilog-AのサブセットがQucsStudioで使用できることが分かりました。それでは、QucsでVerilog-Aを利用するのに適したユースケースを紹介します。

新規半導体デバイスモデル構築

具体例として、ダイオードやトランジスタの簡易モデルが示されています。ですから、こういった用途は非常に適切でしょう。

例えば、自分で作成したデバイスモデルの妥当性検証などはアカデミックで非常に興味深く出来そうです。

モーター駆動シミュレーション

連続時間系のモデルは概ね表現できるので、モーターのモデルも有用でしょう。ハイパワー系トランジスタとモーター駆動のシミュレーションなど、割と興味深い用途が簡単に出来る可能性があります。

適さない利用法

ついでに適さない利用法についても列挙しておきます。

まずは、離散時間に関係するモデルは適しません。例えば、クロックで動作するアナログ回路(サンプル・アンド・ホールドなど)は、cross-eventやif文が活用できないため、記述が難しいと言えます。

次に、領域ごとに数理モデルが異なる場合も適しません。領域を判断し、条件分岐することが、QucsStudioで用いられている実装では難しいためです。

おわりに

今回は、Verilog-Aモデルをフリーの環境で作成する方法を説明してきました。アナログモデルを高位言語で記述することで、要求仕様からスペックに落とし込んでいくことが可能となります。

QucsStudioを用いることで、Verilog-Aの世界を体験することをこの記事では説明しました。制限も分かっている限り明確にしたので、トラブルの対応も比較的楽に出来るでしょう。

この記事が設計の助けになれば幸いです。